# A Novel Cubic Generator Realised by CCIII-based Four Quadrant Analog Multiplier and Divider

### Tajinder Singh Arora<sup>1\*</sup> and R. K. Sharma<sup>2</sup>

<sup>1</sup>Department of Electronics and Communication Engineering, Maharaja Surjamal Institute of Technology, Janakpuri - 110058, New Delhi, India; tajarora@msit.in <sup>2</sup>Department of Electronics and Communication Engineering, Ambedkar Institute of Advanced Communication Technologies and Research, Geeta Colony, Delhi – 110031, India; rksharma.ait@gmail.com

## Abstract

The objective of this paper is to present a novel cubic generator circuit using four quadrant analog multiplier and divider based on third generation current conveyor. A well-established approach has been utilized to implement the new fourquadrant analog multiplier and divider using CCIII exhibiting a larger usable bandwidth. Some additional, relevant, nonlinear applications of CCIII-based four-quadrant analog multiplier and divider have also been worked out to demonstrate its usefulness. PSPICE simulations have been carried out to validate the theoretical findings of the proposed novel cubic generator and other presented circuit configurations. Applications of the new CCIII-based multiplier and divider circuits of this paper have been shown to realize amplitude modulation, squarer and finally the novel cubic generator.

Keywords: Non-Linear circuits, Analog Multiplier, Analog Divider, Third generation current conveyor, Cubic generator

# 1. Introduction

A large number of established research sub-domains of analog signal generation and processing are; continuoustime filters, analog to digital convertors, digital to analog convertors, continuous-time precision rectifiers, inductor realizations, sinusoidal oscillators etc. Further, to realize the desired functionality<sup>1-3</sup> depending upon the specific needs of linear and non-linear application situations, variety of semiconductor devices and integrated circuit Active Building Blocks (ABB) have been employed.

After overwhelming rule of over four decades by operational amplifiers in the design and innovations of linear and non-linear, voltage-mode circuits the currentmode circuits also have taken over. Largely this shift towards current-mode is, arguably, due to the advantages such as; low power consumption, larger dynamic range, greater bandwidth etc<sup>4</sup>. A literature survey reveals that the most popular active building block of this current-mode signal processing has been the Current Conveyor (CC). Till now three generations of CCs and their variants have been available in the literature. For a detailed account on the wide variety of linear and non-linear applications using devices from these current conveyor family readers may refer, for instance<sup>5,6</sup>.

Third generation current conveyor (CCIII) is one of ABBs that has not been explored much for continuoustime signal processing. Although CCIII was introduced long back in 1995 by Fabre<sup>7</sup>, yet very few applications employing CCIII on filters, oscillators, inductor simulation etc<sup>8-12</sup>, have seen day of publication since then.

Four quadrant analog multiplier [FQAM] and divider has historically played a very important role in the area of continuous time signal processing<sup>13,14</sup>. Consequently, a large variety of such circuits were developed employing various ABBs<sup>15-33</sup> such as;operational amplifier<sup>15-17</sup>, operational transconductance amplifier<sup>18</sup>, current conveyor and its variant<sup>19-23</sup>, differential difference amplifer<sup>24</sup>, current feedback operational amplifier<sup>25</sup>, current differencing buffered amplifier<sup>26-27</sup>, current controlled current differencing buffered amplifier<sup>28-29</sup>, current controllable current conveyor transconductance amplifier<sup>32</sup>, operational trans-resistance amplifier<sup>33</sup> etc. This literature survey indicates that no published work of any non-linear application using CCIII can be found in the open literature.

This paper, therefore, attempts to present a novel cubic generator circuit as a non-linear application of third generation current conveyor (CCIII) using a four quadrant analog multiplier and divider. To accomplish this we have considered to use an all CCIII-based analog multiplier and divider in the cubic circuit configuration. The analog multiplier and divider, which works well in all four quadrants, can work without altering the hardware configuration. In order to ensure the effectiveness of this CCIII-based analog multiplier and divider, we have tested it for squarer and amplitude modulator before using them in the new cubic circuit of this paper.

The next section provides the introduction of the used active device i.e CCIII and section 3elaborates the circuit diagram of the new proposed cubic circuit generator along with a detailed approach to design the analog multiplier and dividerand its relevant mathematical development. Section 4 presents the simulation results of all the relevant configuartions and the proposed new cubic circuit. At the end concluding remarks have been given in Section 5.

# 2. Introduction to CCIII

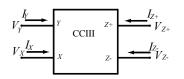

The current conveyor is an active device which can convey the current form one port to another. The third generation current conveyor's port relationship is represented by (1) and its symbollic notation is given in Figure 1.

| $\left[ I_{y} \right]$    | 0       | $-\alpha$   | $ \begin{array}{c} 0 \\ 0 \\ 0 \\ \mathbf{I}_{x} \\ 0 \\ \mathbf{V}_{z\pm} \end{array} \right] $ | (1) |

|---------------------------|---------|-------------|--------------------------------------------------------------------------------------------------|-----|

| $ V_x  =$                 | $\beta$ | 0           | $0 \mid I_x \mid$                                                                                |     |

| $\left[ I_{z\pm} \right]$ | 0       | $\pm\gamma$ | $0 \left\  V_{z\pm} \right\ $                                                                    |     |

where  $\alpha$ ,  $\beta$  and  $\gamma$  represent non-ideal port transfer ratios of X, Y and Z terminals respectively and ideally  $\alpha = \beta = \gamma = 1$ . From (1) we can observe that terminal X and Y are vitually shorted and the current entering through port X will be conveyed to the port Y as well as port Z.

Figure 1. Symbolic Notation of CCIII.

## 3. Cubic Generator Circuit

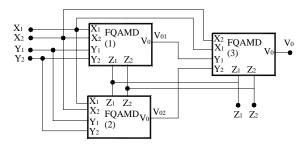

Our innovative approach to the realization of a cubic circuit using the four quadrant analog multiplier and divider (FQAMD) is shown in Figure 2 which is a complete CCIII-based cubic circuit generator. The detailed description comprising of mathematical development of the FQAMD block has been given in next subsection.

**Figure 2.** Cubic circuit realization using four quadrant analog multiplier/divider.

The outputs of the three FQAMD blocks are  $V_{01}$ ,  $V_{02}$  and  $V_0$  respectively given in (2)-(4) and the final output of the cubic circuit is represented by (5)-(6).

$$V_{01} = \frac{(W_A/L_A) (X_1 - X_2)(Y_1 - Y_2)}{(W_B/L_B)(Z_1 - Z_2)}$$

(2)

$$V_{02} = \frac{(W_A/L_A) (X_1 - X_2)(Y_2 - Y_1)}{(W_B/L_B)(Z_1 - Z_2)}$$

(3)

$$V_{0} = \frac{(W_{A}/L_{A}) (X_{1} - X_{2})^{2} (Y_{1} - Y_{2})}{(W_{B}/L_{B})(Z_{1} - Z_{2})}$$

(4)

If

$$X_1 = Y_1$$

and  $X_2 = Y_2$  then

$$V_{0} = \frac{(W_{A}/L_{A}) (X_{1} - X_{2})^{3}}{(W_{B}/L_{B})(Z_{1} - Z_{2})^{2}}$$

(5)

If the aspect ratios of the MOSFETs employed in FQAMD are kept same, the circuit acts as cubic circuit and the output is given as.

$$V_0 = \frac{(X_1 - X_2)^3}{(Z_1 - Z_2)^2}$$

(6)

## 3.1 Four Quadrant Analog Multiplier and Divider employing CCIII

The complete circuit diagram of FQAMD block used in the proposed cubic circuit of Figure 2, which is simultaneously a multiplier and a divider is shown in Figure 3.

Figure 3. Four Quadrant Analog Multiplier/Divider employing CCIII.

Here, a well-established approach<sup>14</sup> has been considered to deduce the FQAMD of Figure 3 using CCIII where all MOS transistors are operating in triode region. The drain current equation for the MOS transistor, working in triode region, is given by (7).

$$I_{D} = K \left[ (V_{GS} - V_{TH}) V_{DS} - \frac{V_{DS}^{2}}{2} \right]$$

(7)

Where  $K = \mu . Cox (W/L)$

Let the current flowing from  $M_1$  and  $M_2$  is  $I_{D1}$ , given in (8), the current flowing from  $M_3$  and  $M_4$  is  $I_{D2}$ , represented in (9) and the current flowing through  $M_5$  and  $M_6$  is  $I_{D3}$  and  $I_{D4}$  expressed by (10) and (11) respectively.

$$I_{D1} = K \left[ (X_1 - V_{TH}) Y_1 - \frac{Y_1^2}{2} \right] + K \left[ (X_2 - V_{TH}) Y_2 - \frac{Y_2^2}{2} \right]$$

(8)

$$I_{D2} = K \left[ (X_2 - V_{TH})Y_1 - \frac{Y_1^2}{2} \right] + K \left[ (X_1 - V_{TH})Y_2 - \frac{Y_2^2}{2} \right]$$

(9)

$$I_{D3} = K \left[ (Z_2 - V_{TH}) V_0 - \frac{V_0^2}{2} \right]$$

(10)

$$I_{D4} = K \left[ (Z_1 - V_{TH}) V_0 - \frac{V_0^2}{2} \right]$$

(11)

Now considering the aspect ratios of MOS transistors  $M_1$  to  $M_4$  as  $(W_A/L_A)$  and that of  $M_5$  and  $M_6$  as  $(W_B/L_B)$ , by routine analysis, the output voltage  $(V_0)$  can be written as given in (12), where, again, all the utilized NMOS transistors are assumed to be operating in the triode region.

$$V_{0} = \frac{(W_{A}/L_{A}) (X_{1} - X_{2})(Y_{1} - Y_{2})}{(W_{B}/L_{B})(Z_{1} - Z_{2})}$$

(12a)

or

$$V_{0} = \frac{(W_{A}/L_{A}) \Delta X.\Delta Y}{(W_{B}/L_{B})\Delta Z}$$

(12b)

where  $\Delta X = X_1 - X_2$  and  $\Delta Y = Y_1 - Y_2$  and  $\Delta Z = Z_1 - Z_2$ .

Now, again, if the aspect ratios, of all the used MOS transistors, are considered to have the same value, then the expression for the output voltage is independent of the MOS transistor parameters. Thus, for  $V_T$  being the threshold voltage of the MOSFETs, following conditions needs to be satisfied for them to operate in triode region.

$$Y_1, Y_2 \le \min [(X_1 - V_T), (X_2 - V_T)] \text{ for } M_1 \text{ to } M_4$$

(13)

and

$$V_0 \le \min [(Z_1 - V_T), (Z_2 - V_T)]$$

for  $M_5 \& M_6$  (14)

The FQAMD circuit of Figure 3 works as a four quadrant multiplier when, X and Y terminal acts as input terminals and at Z terminal some controlled voltage is applied. In such a case,  $V_0$  is the result of multiplication of potential difference  $(X_1 - X_2)$ ,  $(Y_1 - Y_2)$  with some constant gain. If  $X_1$  and  $X_2$  are of the form (X + x) and (X - x) respectively, where X is the DC component while x is the signal component and if Y1 and Y2 are defined by the relation i.e.  $Y_1$ =- $Y_2$ = y again being another signal component with Z terminal having  $Z_1$ = $V_{z1}$  and  $Z_2$ = $V_{z2}$ , both being DC control voltages then

$$V_{0} = \frac{4. (W_{A}/L_{A}) x. y}{(W_{B}/L_{B})(V_{z1}-V_{z2})}$$

(15)

Additionally, (12a) represents a divider when either of the potential differences  $(X_1-X_2)$  or  $(Y_1-Y_2)$  is kept constant, say  $(X_1-X_2)$  in this case. This  $(X_1-X_2)$  acts as constant gain along with the gain provided by transistor aspect ratios. Now,  $V_0$  is the result of the divider with some constant gain.

This FQAMD, the multiplier and divider configuration, has been utilized in Figure 2 to build the cubic circuit.

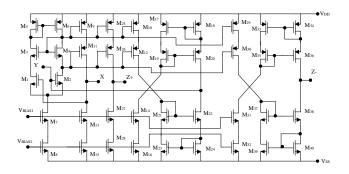

## 4. Simulation Results

We present now, in the following, the SPICE simulation validations for the multiplier, divider and the cubic circuit. Additionally, we have also shown SPICE simulations for squarer and an amplitude modulator to further establish the working of the FQAMD realization of the Figure 3. The CMOS CCIII structure of<sup>34</sup> used here is redrawn in Figure 4. The aspect ratios of these MOS transistors are given in Table 1. We have used 0.35µm, level 3 CMOS model parameter for the testing the above mentioned configurations which are given in Table 2. The supply voltage considered is  $V_{DD} = -V_{SS} = 1.6V$  and values of the bias voltages are  $V_{BIAS1} = -0.38V$  and  $V_{BIAS2} = -0.9V$ .

Figure 4. Third generation current conveyor (CCIII)<sup>34</sup>.

| Table 1. | Aspect ratios of the MOSFETs of CCIII of |

|----------|------------------------------------------|

| Figure 4 |                                          |

| CMOS transistors               | W/L (in $\mu/m$ ) |

|--------------------------------|-------------------|

| M1-M4                          | 10/0.35           |

| M5,M6                          | 16/0.35           |

| M7, M8, M13-M16, M21-M24,      | 16/0.35           |

| M27,M28, M31, M32, M37-M40     |                   |

| M9-M12,M17-M20, M25, M26, M29, | 30/0.35           |

| M30, M33-M36                   |                   |

In the following we give separately the detailed account

of the simulations of various tested configurations namely; multiplier, divider, squarer, amplitude modulator and cubic circuit. We have also given in the end a frequency response characteristic of the FQAMD.

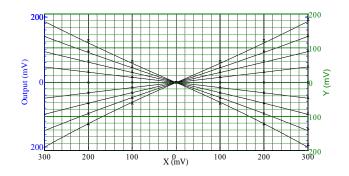

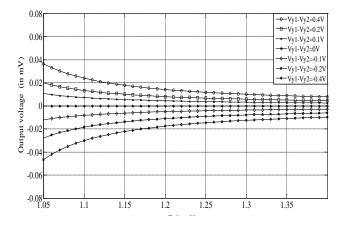

#### 4.1 Multiplier

For the simulation purpose value of X was taken to be 3V while x was varied from -300mV to +300mV. The potential difference  $(Y_1 - Y_2)$  was varied from -200mV to +200mV.  $V_{Z1}$  and  $V_{Z2}$  were kept constant at 4.1V and 2.85V respectively, maintaining a constant potential difference of 1.25V. All transistor aspect rations were kept same as W/L = 1.05µm /0.35µm. Now the output potential was plotted for different values of  $(Y_1 - Y_2)$ . The output waveform of the, circuit given in Figure 3 when acts as a four-quadrant multiplier, is shown in Figure 5. In Figure 5 'cross marked' sign shows the theoretical output whereas continuous line represents simulated output. As can be seen in the Figure 5, the results are in agreement with the theoretical results to a high degree.

**Figure 5.** DC transfer characteristics of the designed circuit as a FQAM.

| Table 2. 0.55 µmCMOS process parameters utilized in simulation                 |

|--------------------------------------------------------------------------------|

| .MODEL NMOS1 NMOS (LEVEL = 3                                                   |

| + TOX = 7.9E-9 NSUB = 1E17 GAMMA = 0.5827871                                   |

| + PHI = 0.7 VTO = 0.5445549 DELTA = 0 UO = 436.256147 ETA = 0                  |

| +THETA = 0.1749684 KP = 2.055786E-4 VMAX = 8.309444E4 KAPPA = 0.2574081        |

| + RSH =0.0559398 NFS = 1E12 TPG = 1 XJ = 3E-7 LD = 3.162278E-11                |

| +WD = 7.046724E-8 CGDO = 2.82E-10 CGSO = 2.82E-10 CGBO= 1E-10                  |

| +CJ = 1E-3 PB = 0.9758533 MJ = 0.3448504 CJSW = 3.777852E-10 MJSW = 0.3508721) |

| .MODEL PMOS1 PMOS (LEVEL = 3                                                   |

| + TOX = 7.9E-9 NSUB = 1E17 GAMMA = 0.4083894                                   |

| + PHI = 0.7 VTO = -0.7140674 DELTA =0 UO = 212.2319801 ETA = 9.999762E-4       |

| +THETA = 0.2020774 KP = 6.733755E-5 VMAX = 1.181551E5 KAPPA = 1.5              |

| +RSH =30.0712458 NFS = 1E12 TPG = -1 XJ = 2E-7 LD = 5.000001E-13               |

| +WD = 1.249872E-7 CGDO = 3.09E-10 CGSO = 3.09E-10 CGBO = 1E-10                 |

| +CJ = 1.419508E-3 PB = 0.8152753 MJ = 0.5 CJSW = 4.813504E-10 MJSW = 0.5)      |

Table 2.

$0.35 \ \mu m$ CMOS process parameters utilized in simulation

#### 4.2 Divider

For the purpose of simulation, the values taken were  $X_1 = 3V$ ,  $X_2 = 2.95V$  (making the potential difference  $(X_1 - X_2) = 50$  mV). All transistor aspect rations were kept same as W/L =  $1.05\mu$ m / $0.35\mu$ m. Now the output potential was plotted for five different values of  $(Y_1 - Y_2)$ . The SPICE plot showing the division output using the above values is given in Figure 6.

**Figure 6.** DC transfer characteristics of the designed circuit as a Four Quadrant Analog Divider.

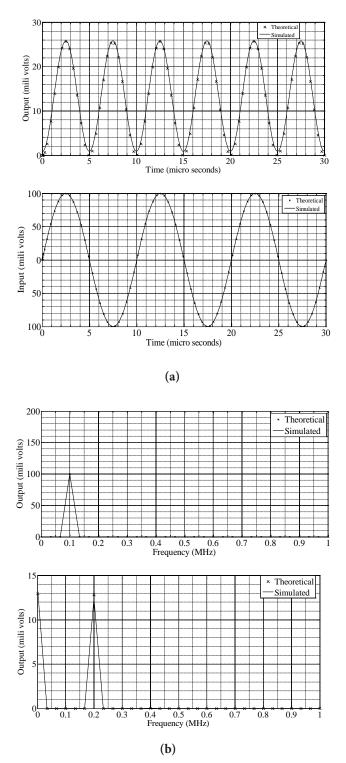

#### 4.3 Squarer

In order for the circuit to act as a squarer, the potential difference  $(Z_1-Z_2)$  must be kept constant, while the potential difference  $(X_1-X_2)$  and  $(Y_1-Y_2)$  must be kept same and equal to the required squarer input. During the simulation the values of these potentials were  $V_{Z1} = 2.5V$ ,  $V_{z_2} = 1.25V$  (thus making the potential difference  $(Z_1 - Z_2)$ ) = 1.25V).  $X_1$  and  $X_2$  were taken to be of the form (X+x) and (X-x) respectively where X was taken as a constant DC voltage (2.5V) while x was taken to be a sinusoidal wave of 100mV and 100 KHz frequency. Similarly, Y<sub>1</sub> and Y<sub>2</sub> were taken to be of the form (y) and (-y) respectively where y was taken as a sinusoidal wave of 100mV amplitude and 100 KHz frequency. Thus, both the potential differences  $(X_1-X_2)$  and  $(Y_1-Y_2)$  were sinusoidal waves of 200mV amplitude and 100 KHz frequency which acted as the input to squarer. The transistor aspect rations were same as used in previous case. The simulation result is shown in Figure 7 which resembles the theoretical result to a high degree.

**Figure 7.** DC transfer characteristics of the designed circuit as a Four Quadrant Analog Divider.

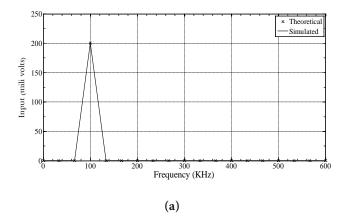

#### 4.4 Amplitude Modulator

In order for the circuit to act as an amplitude modulator, the potential difference  $(Z_1-Z_2)$  must be kept constant, while the carrier signal and modulating signal must be applied at  $(X_1-X_2)$  and  $(Y_1-Y_2)$ . During the simulation, the values of these potentials were  $Z_1 = 2.5V$ ,  $Z_2 = 1.25V$  (thus making the potential difference  $(Z_1-Z_2) = 1.25V$ ). X<sub>1</sub> and X<sub>2</sub> were taken to be of the form (X+x) and (X-x) respectively where X was taken as a constant DC voltage (1.25V) while x was taken to be a sinusoidal wave of 100mV amplitude and 100KHz frequency. Thus the potential difference (X<sub>1</sub>-X<sub>2</sub>) acted as a carrier wave of 200mV, 10KHz frequency. Similarly, Y<sub>1</sub> and Y<sub>2</sub> were taken to be of the form y and -y respectively where y was taken as a sinusoidal wave of amplitude 100mV and 100 KHz frequency. Thus, the potential differences  $(Y_1 - Y_2)$  acted as a modulating wave of 200mV and 100 KHz frequency. The transistor aspect rations were same as used in previous case. The simulation result is shown in Figure 8, which match the theoretical results.

**Figure 8.** Simulation results of the proposed circuit as an amplitude modulator (AM) circuit (a) time –domain response (b) frequency domain response.

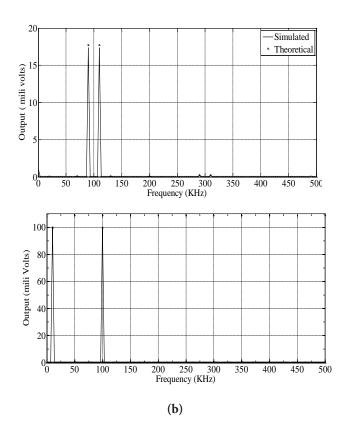

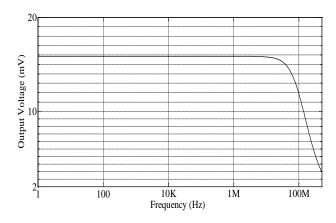

# 4.5 Frequency response characteristic of the FQAMD

In order to obtain the frequency response of the FQAMD circuit, the values of the input potentials were chosen to be  $V_{Z1} = 4.1V$ ,  $V_{Z2} = 2.85V$  (making  $Z_1$ - $Z_2 = 1.25V$ ),  $Y_1 = 250$ mV,  $Y_2 = -250$ mV (making  $Y_1$ - $Y_2 = 500$ mV).  $X_1$  and  $X_2$  were taken to be of the form (X+x) and (X-x) respectively where X was taken as a constant DC voltage (0.25V) while x was taken to be a sinusoidal wave of 0.5mV and varying frequency (making  $X_1$ - $X_2$  to be sinusoidal wave of amplitude 1mV and varying frequency). The output potential was plotted against the frequency to obtain the frequency response shown in Figure 9. By simulation we have obtained the bandwidth to be 112.63MHz.

**Figure 9.** Frequency response of the proposed FQAMD circuit.

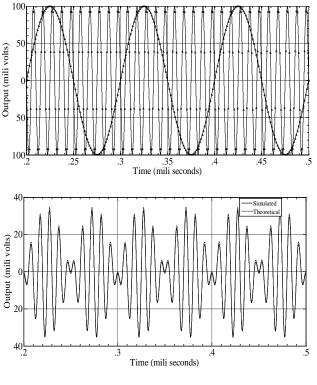

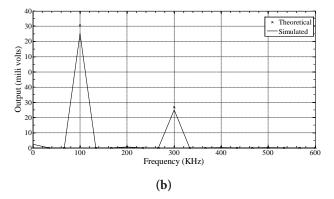

#### 4.6 Cubic Circuit

For testing the functionality of the cubic circuit generator, three FQAMD blocks have been employed as shown in Figure 2. The outputs of the FQAMD circuits have been used as an input to the 3<sup>rd</sup> block of FQAMD. The final output is the output of the 3rd block of FQAMD. For simulation purposes, X1 and X2 were taken to be of the form (X+x) and (X-x) respectively where X was taken as a constant DC voltage (2.5V) while x was taken to be a sinusoidal wave of 100mV and 100 KHz frequency. Thus, both the potential differences  $(X_1-X_2)$  was sinusoidal waves of 200mV amplitude and 100 KHz frequency which acted as the input to cubic circuit. During the simulation the values of these potentials were  $V_{71} = 2.5V_{71}$  $V_{72}$  = 1.25V. The transistor aspect rations were constant as used in previous case. The simulation result is shown in Figure 10, which validates the working of the circuit as a cubic generator.

Figure 10. Frequency domain response of the proposed circuit as a cubic circuit (a) input waveform (b) output waveform.

The above simulation results demonstrate the validity of the theoretical assertions of the realized new cubic circuit. The simulations also justify the results of multiplier, divider, squarer and the amplitude modulator. The frequency response of our FQAMD shown in Figure 9 demonstrates improvement with respect to the frequency response one recent related work<sup>27</sup>.

## 5. Conclusion

A complete CCIII-based new cubic circuit has been presented which fills to some extent the void of a CCIIIbased non-linear applications. The cubic circuit presented utilized our CCIII-based FQAMD circuit derived from that of<sup>14</sup>. Other non-linear applications of the presented CCIII-based FQAMD namely; multiplier, divider, squarer and amplitude modulator were also tested and found to be working as expected. All worked out PSPICE simulations validate the theoretical results of the proposed configurations.

## 6. References

- Allen PE, Holberg DR. CMOS analog circuit design. Oxford Univ. Press; 2002.

- 2. Razavi B. Design of Analog CMOS Integrated Circuits. Tata McGraw-Hill Education; 2002 Oct 1.

- Schaumann R, Ghausi MS. Design of Analog Filters: Passive, Active RC and Switched Capacitors. Prentice Hall Press, (USA), 1990.

- Wilson B. Recent developments in current conveyors and current-mode circuits. IEE Proceedings G-Circuits, Devices and Systems. 1990 Apr; 137(2):63–77.

- Mohan PA. Current-mode VLSI analog filters: design and applications. Springer Science & Business Media; 2012 Dec 6.

- Senani R, Bhaskar DR, Singh AK. Current conveyors: variants, applications and hardware implementations. Springer; 2014 Oct 9.

- Fabre A. Third-generation current conveyor: a new helpful active element. Electronics Letters. 1995 Mar 2; 31(5):338– 9.

- Cam U. A new trans admittance type first-order all pass filter employing single third generation current conveyor. Analog Integrated Circuits and Signal Processing. 2005 Apr 1; 43(1):97–9.

- 9. Hwang YS, Chen JJ, Li JP. New current-mode all-pole and elliptic filters employing current conveyors. Electrical Engineering. 2007 Jun 1; 89(6):457–9.

- Kuntman H, Gulsoy M, Cicekoglu O. Actively simulated grounded lossy inductors using third generation current conveyors. Microelectronics Journal. 2000 Apr 30; 31(4):245–50.

- Sharma R, Arora TS, Senani R. On the Realisation of Canonic Single-Resistance-Controlled Oscillators using Third Generation Current conveyors. IET Circuits, Devices and Systems. 2016 Jul 20.

- Arora TS, Sharma RK. Realization of current mode KHN-equivalent biquad employing third generation current conveyor. 2016 International Conference on Computational Techniques in Information and Communication Technologies (ICCTICT), IEEE. 2016 Mar 11. p. 558–62.

- Gilbert B. A precise four-quadrant multiplier with sub nanosecond response. IEEE Journal of Solid-State Circuits. 1968 Dec; 3(4):365–73.

- 14. Khachab NI, Ismail M. MOS multiplier/divider cell for analogue VLSI. Electronics Letters. 1989 Nov 9; 25(23):1550–2.

- Khachab NI, Ismail M. A nonlinear CMOS analog cell for VLSI signal and information processing. IEEE Journal of Solid-State Circuits. 1991 Nov; 26(11):1689–99.

- Ismail M, Brannen R, Takagi S, Fujii N, Khachab NI, Khan R, Aaserud O. Configurable CMOS multiplier/divider circuits for analog VLSI. Analog Integrated Circuits and Signal Processing. 1994 May 1; 5(3):219–34.

- 17. Riewruja V, Rerkratn A. Four-quadrant analogue multiplier using operational amplifier. International Journal of Electronics. 2011 Apr 1; 98(4):459–74.

- Kaewdang K, Fongsamut C, Surakampontorn W. A wideband current-mode OTA-based analog multiplier-divider. Proceedings of the 2003 International Symposium on Circuits and Systems, 2003. ISCAS'03, IEEE. 2003 May 25; 1:I–349.

- Liu SI, Wu DS, Tsao HW, Wu J, Tsay JH. Nonlinear circuit applications with current conveyors. IEE Proceedings G-Circuits, Devices and Systems. 1993 Feb; 140(1):1–6.

- 20. Premont C, Cattet S, Grisel R, Abouchi N, Chante JP, Renault D. A CMOS multiplier/divider based on current conveyors. Proceedings of the 1998 IEEE International Sym-

posium on Circuits and Systems, 1998. ISCAS'98. 1998; 1:69-71.

- 21. Premont C, Abouchi N, Grisel R, Chante JP. A BiCMOS current conveyor based four-quadrant analog multiplier. Analog integrated circuits and signal processing. 1999 May 1; 19(2):159–62.

- 22. Ali MT. A current-mode current-controlled current-conveyor-based analogue multiplier/divider. International Journal of Electronics. 1998 Jul 1; 85(1):71–7.

- 23. Yuce E. Design of a simple current-mode multiplier topology using a single CCCII+. IEEE Transactions on Instrumentation and Measurement. 2008 Mar; 57(3):631–7.

- Huang SC, Ismail M. Design and applications of a CMOS analog multiplier cell using the differential difference amplifier. Analog Integrated Circuits and Signal Processing. 1994 Nov 1; 6(3):209–17.

- 25. Liu SI, Chen JJ. Realization of analogue divider using current feedback amplifiers. IEE Proceedings. Circuits, Devices and Systems. 1995; 142(1):45–8.

- Keskin AU. A four quadrant analog multiplier employing single CDBA. Analog Integrated Circuits and Signal Processing. 2004 Jul 1; 40(1):99–101.

- 27. Pathak JK, Singh AK, Senani R. New Multiplier/Divider using a Single CDBA. American Journal of Electrical and Electronic Engineering. 2014 Jan 23; 2(3):98–102.

- 28. Siripruchyanun M. A design of analog multiplier and divider using current controlled current differencing buffered amplifiers. 2007 International Symposium on Integrated Circuits, IEEE. 2007 Sep 26; 568–71.

- 29. Jaikla W, Siripruchyanun M. Novel current-mode four-quadrant Multiplier/divider based on current controlled CDBAs (CCCDBAs). In the 3rd ECTI Annual Conference. 2006. p. 509–12.

- Siripruchyanun M, Jaikla W. A current-mode analog multiplier/divider based on CCCDTA. AEU-International Journal of Electronics and Communications. 2008 Mar 3; 62(3):223–7.

- 31. Tangsrirat W, Pukkalanun T, Mongkolwai P, Surakampontorn W. Simple current-mode analog multiplier, divider, square-rooter and squarer based on CDTAs. AEU-International Journal of Electronics and Communications. 2011 Mar 31; 65(3):198–203.

- Woratraijariya P, Mano K, Jaikla W, Maneewan S. Current-mode 4 quadrant divider employing only single active element. 2012 IEEE International Conference on Electron Devices and Solid State Circuit (EDSSC), IEEE. 2012 Dec 3. p. 1–4.

- 33. Pandey R, Pandey N, Sriram B, Paul SK. Single OTRA based analog multiplier and its applications. ISRN Electronics. 2012 Nov 14.

- 34. Arora TS, Sharma RK. Adjoint-KHN Equivalent Realization of Current Mode Universal Biquad Employing Third Generation Current Conveyor. Indian Journal of Science and Technology. 2016 Apr 14; 9(13):1–8.